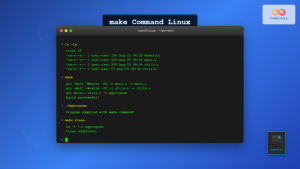

In the world of C programming, efficiency is key. As projects grow larger and more complex, manually compiling each source file becomes a tedious and error-prone task. Enter the makefile: a powerful tool that automates the compilation process, saving time and reducing mistakes. In this comprehensive guide, we'll dive deep into the world of C makefiles, exploring their structure, syntax, and best practices.

Understanding Makefiles

A makefile is a special file, typically named Makefile (with a capital 'M'), that contains a set of directives used by the make utility to build and manage C projects. It defines rules for compiling source files, linking object files, and creating the final executable.

🔍 Key Concept: Makefiles allow you to define dependencies between files and specify how to generate target files from their dependencies.

Basic Makefile Structure

Let's start with a simple example to illustrate the basic structure of a makefile:

CC = gcc

CFLAGS = -Wall -Wextra -std=c11

hello: hello.o

$(CC) $(CFLAGS) -o hello hello.o

hello.o: hello.c

$(CC) $(CFLAGS) -c hello.c

clean:

rm -f hello hello.o

Let's break down this makefile:

CC = gcc: Defines the C compiler to use.CFLAGS = -Wall -Wextra -std=c11: Sets compiler flags for warnings and C standard.hello: hello.o: Specifies that thehellotarget depends onhello.o.$(CC) $(CFLAGS) -o hello hello.o: The command to create thehelloexecutable.hello.o: hello.c: Indicates thathello.odepends onhello.c.$(CC) $(CFLAGS) -c hello.c: The command to compilehello.cintohello.o.clean:: A target to remove generated files.rm -f hello hello.o: The command to remove the executable and object file.

Makefile Rules

Each rule in a makefile follows this general format:

target: dependencies

commands

target: The file to be created or the action to be executed.dependencies: Files that the target depends on.commands: Shell commands to create the target (must be indented with a tab).

🚀 Pro Tip: Use .PHONY to declare targets that don't represent files, like clean:

.PHONY: clean

clean:

rm -f *.o hello

Variables in Makefiles

Variables in makefiles make your build process more flexible and easier to maintain. Here's an expanded example:

CC = gcc

CFLAGS = -Wall -Wextra -std=c11

LDFLAGS = -lm

SOURCES = main.c helper.c

OBJECTS = $(SOURCES:.c=.o)

EXECUTABLE = myprogram

$(EXECUTABLE): $(OBJECTS)

$(CC) $(CFLAGS) $(OBJECTS) -o $@ $(LDFLAGS)

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -f $(OBJECTS) $(EXECUTABLE)

In this example:

SOURCESlists all source files.OBJECTSuses a substitution reference to create a list of object files.$@is an automatic variable representing the target.$<is an automatic variable representing the first dependency.- The

%.o: %.crule is a pattern rule for compiling any.cfile into a.ofile.

Conditional Statements in Makefiles

Makefiles support conditional statements, allowing you to customize the build process based on certain conditions. Here's an example:

CC = gcc

CFLAGS = -Wall -Wextra

ifdef DEBUG

CFLAGS += -g -DDEBUG

else

CFLAGS += -O2

endif

SOURCES = main.c helper.c

OBJECTS = $(SOURCES:.c=.o)

EXECUTABLE = myprogram

$(EXECUTABLE): $(OBJECTS)

$(CC) $(CFLAGS) $(OBJECTS) -o $@

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -f $(OBJECTS) $(EXECUTABLE)

In this makefile, if DEBUG is defined (e.g., by running make DEBUG=1), debug flags are added; otherwise, optimization is enabled.

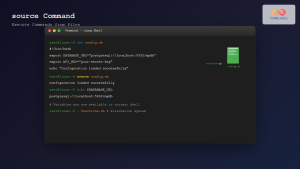

Functions in Makefiles

Make provides several built-in functions to manipulate text. Here's an example using some common functions:

CC = gcc

CFLAGS = -Wall -Wextra

SOURCES = $(wildcard *.c)

OBJECTS = $(patsubst %.c,%.o,$(SOURCES))

EXECUTABLE = $(notdir $(CURDIR))

$(EXECUTABLE): $(OBJECTS)

$(CC) $(CFLAGS) $(OBJECTS) -o $@

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -f $(OBJECTS) $(EXECUTABLE)

print:

@echo "Source files: $(SOURCES)"

@echo "Object files: $(OBJECTS)"

@echo "Executable: $(EXECUTABLE)"

In this example:

wildcardfunction finds all.cfiles in the current directory.patsubstfunction replaces.cextensions with.o.notdirfunction extracts the current directory name for the executable.

Advanced Makefile Techniques

Automatic Dependency Generation

For large projects, manually tracking all dependencies can be challenging. GCC can generate dependency files automatically:

CC = gcc

CFLAGS = -Wall -Wextra -MMD -MP

SOURCES = $(wildcard *.c)

OBJECTS = $(SOURCES:.c=.o)

DEPS = $(OBJECTS:.o=.d)

EXECUTABLE = myprogram

$(EXECUTABLE): $(OBJECTS)

$(CC) $(CFLAGS) $(OBJECTS) -o $@

-include $(DEPS)

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -f $(OBJECTS) $(DEPS) $(EXECUTABLE)

The -MMD and -MP flags generate dependency files, and -include $(DEPS) includes them in the makefile.

Recursive Make

For projects with multiple directories, you can use recursive make:

SUBDIRS = src lib tests

all: $(SUBDIRS)

$(SUBDIRS):

$(MAKE) -C $@

clean:

for dir in $(SUBDIRS); do \

$(MAKE) -C $$dir clean; \

done

.PHONY: all $(SUBDIRS) clean

This makefile will enter each subdirectory and run the make command there.

Best Practices for C Makefiles

-

Use Variables: Define common values like compiler and flags as variables for easy modification.

-

Employ Pattern Rules: Use pattern rules (like

%.o: %.c) to avoid repetition. -

Declare Phony Targets: Use

.PHONYfor targets that don't represent files. -

Generate Dependencies Automatically: Use compiler flags to generate and include dependency files.

-

Keep It Modular: For large projects, use separate makefiles for different components and combine them with recursive make.

-

Use Conditional Compilation: Implement debug and release builds using conditional statements.

-

Document Your Makefile: Add comments to explain complex rules or variables.

-

Test Your Makefile: Ensure it works correctly for clean builds, incremental builds, and different targets.

Conclusion

Makefiles are an essential tool in any C programmer's toolkit. They automate the build process, manage dependencies, and make large projects manageable. By mastering makefiles, you'll save time, reduce errors, and create more maintainable C projects.

Remember, the examples provided here are just the tip of the iceberg. As you work on more complex projects, you'll discover even more powerful features of makefiles. Keep experimenting, and don't hesitate to consult the GNU Make manual for advanced techniques.

Happy coding, and may your builds always be successful! 🖥️💻🚀